「半導体」という言葉がニュースや新聞で多く出てきます。

コロナ禍に起きた半導体不足によって世間でも半導体の認知度と重要性が広がりました。そんな半導体ですが、トランジスタと呼ばれる素子が集積することで構成されています。

またラピダスという会社が設立され、日本国内で先端半導体を製造することが目指されています。

- 半導体に興味関心がある

- そもそもトランジスタとは?を知りたい方

- トランジスタの微細化がどこまで続くのかを知りたい方

この記事ではトランジスタの基本とまだまだ進んでいる微細化について誰にでもわかるように解説します。

ぜひとも最後までご覧ください。

【プロフィール】

- 上場企業の現役半導体プロセスエンジニア

(経験10年以上) - 多くの材料メーカーや生産委託先企業との業務経験あり

- 著書を出版しました

- 詳しいプロフィールはこちらからどうぞ

動画で解説:トランジスタと微細化の基本

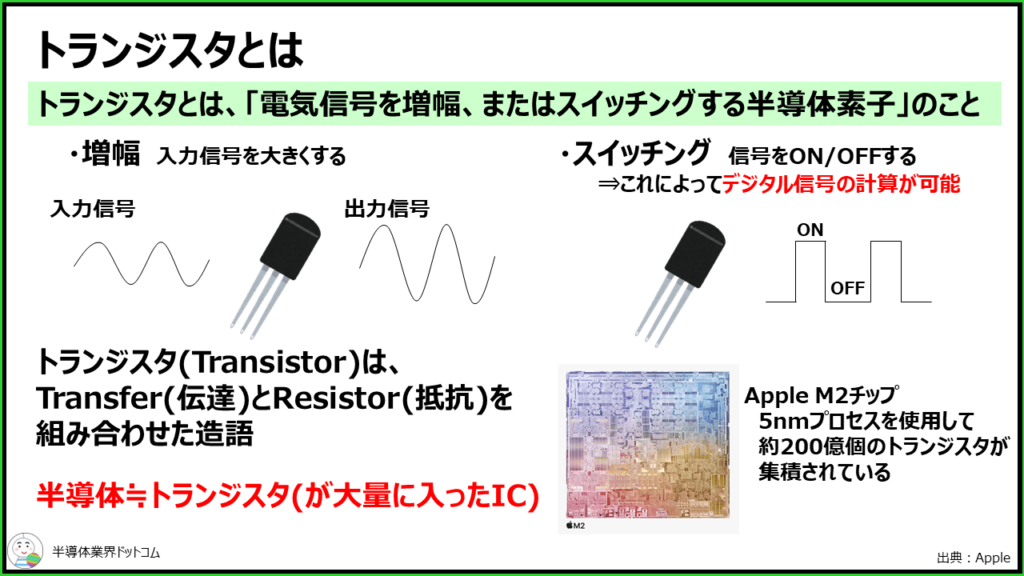

トランジスタとは電気信号を増幅、スイッチングする半導体素子のこと

トランジスタは半導体デバイスの主役と言える素子のことです。

トランジスタが持つ機能は2つあり、情報処理に使用される電気信号を

- 増幅する(入力された信号を大きくする)

- スイッチングする(信号をオン/オフする)

増幅とは入力された小さな信号を大きくすることで、マイクやスピーカーを想像してもらえると分かりやすいです。

スイッチングとは信号をオン/オフすることで、部屋の電気のスイッチをイメージしてもらえると分かりやすいです。部屋の電気はオンすると電気が付いて、オフすると電気が消えます。トランジスタでは電気信号をオン/オフすることで、デジタル信号の計算や記憶が可能になります。

トランジスタ(Transistor)の名称の由来は、Transfer(伝達)とResistor(抵抗)を組み合わせた造語です。

世間一般で使われる「半導体」という言葉は、このトランジスタが大量に集積されたIC(Integrated Circuit:集積回路)のことを指しています。例えばAppleのiPhoneやMacに搭載されているM2チップでは5nmプロセスを使用しておよそ200億個ものトランジスタが集積されています。

トランジスタは米国ベル研究所で発明された

トランジスタは20世紀最大の発明品の1つに数えられます。

ベル研究所(ベル研)は電気通信分野の基礎技術に関する研究開発を行っていたアメリカの研究所です。その名前の通り、電話を発明したグラハム・ベルが設立したアメリカ電話電信会社(AT&T)傘下の研究所でした。

1930年代、AT&T社は全米に長距離の電話通信網を建設していました。しかし、電話の声(音声信号)はある程度の距離を経ると減衰して小さくなってしまうため、信号を大きくする増幅をさせる必要がありました。そのために当時は数多くの真空管を使用していました。しかし、真空管は寿命が短いため故障によるトラブルが多く、改善の必要に迫られていました。

そのため真空管を代替することができるデバイスの開発がベル研で始まりました。ベル研ではウィリアム・ショックレーをリーダーとした研究チームが作られ、そこに理論物理学者ジョン・バーディーンと実験物理学者ウォルター・ブラッテンらが加わりました。研究は第2次世界大戦で一時的に中断しましたが、半導体材料であるゲルマニウムを使って、電流の増幅作用が生まれることを発見しました。これが点接触型トランジスタと呼ばれる初期のトランジスタで、現在のバイポーラ型と呼ばれるトランジスタの原型です。トランジスタの公式な発明日は1947年12月23日とされています。

トランジスタの発明によってショックレー、バーディーン、ブラッテンの3名は1956年にノーベル物理学賞を受賞しています。授賞理由は「半導体の研究およびトランジスタ効果の発見」です。

なおバーディーンはその後、超電導の理論的な研究を行い、1972年に2度目のノーベル物理学賞を受賞しました。現在、ノーベル物理学賞を2度受賞した唯一の人物です。

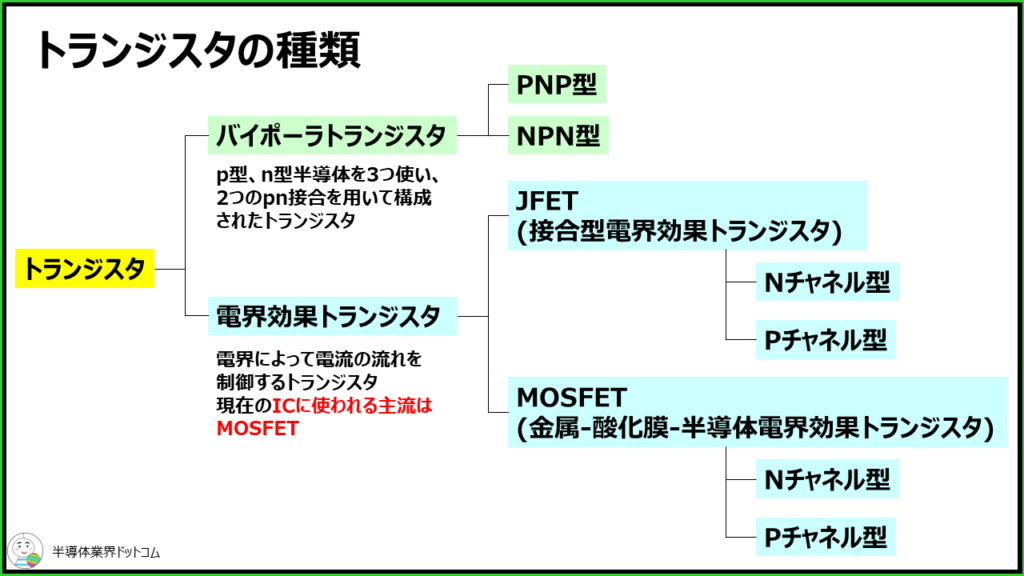

トランジスタの種類

トランジスタはその動作原理からバイポーラトランジスタと電界効果トランジスタの大きく2種類に分類されます。

バイポーラトランジスタのバイポーラの由来は、電気伝導に関わるキャリアが電子と正孔の2つ(2を意味するラテン語がバイ)の極性(ポール)であるためです。

バイポーラトランジスタの構造はn型半導体とp型半導体をお互いに挟み込んだ、サンドイッチにしたnpn型とpnp型に分類されます。バイポーラトランジスタの特徴は電流駆動型デバイスであり、動作させるのに必要な電力、すなわち消費電力が大きくなります。スイッチング速度は低く、トランジスタ面積は大きくなります。あまりメリットがないように見えますが、一部のアナログ回路用ICなどで使用されています。

電界効果トランジスタはその中でさらにJFETとMOSFETに分類されます。一般的に使用されるのはMOS型です。

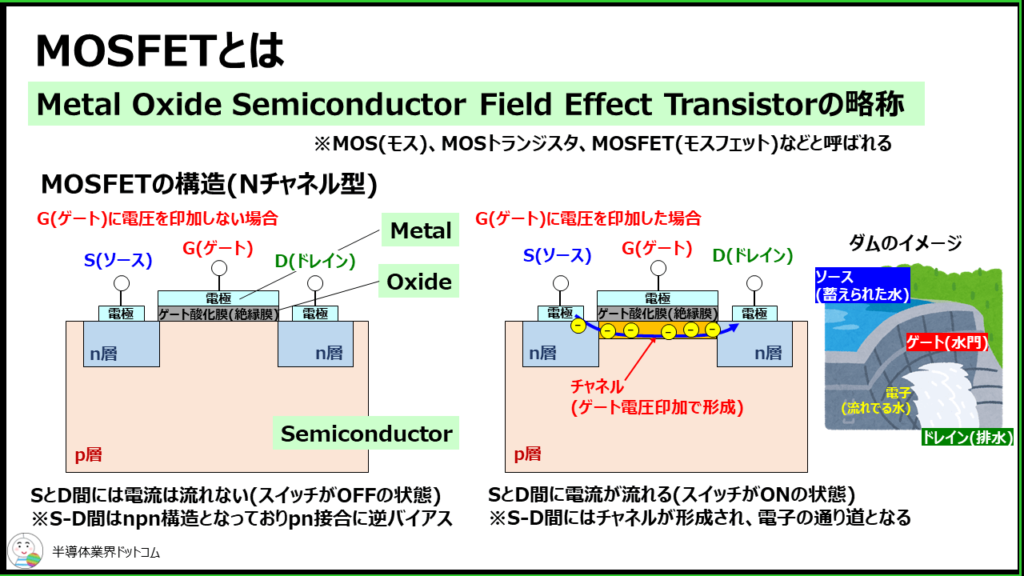

MOS型トランジスタのMOSとはその構造がMetal(金属)-Oxide(酸化膜)-Semiconductor(半導体)の3層構造をしていることに由来しています。電気伝導に関わるキャリアが電子だけですので、バイポーラ型と対比させてユニポーラ型とも呼ばれます(1を意味するラテン語がユニ)。MOS型はゲート電圧により流れる電流制御されるチャネル内のキャリアによってpチャネル型とnチャネル型に分類されます。MOS型の特徴は電圧駆動型のデバイスであり、消費電力を小さくできます。スイッチング速度が速くトランジスタ面積を小さくできるため現在、ICを構成するメインデバイスとして広く使用されています。

MOSFETとは

一般に広く使用されているトランジスタはMOSFETです。

MOSFETはMetal Oxide Semiconductor Field Effect Transistorの略称で、「モス」や「モスFET」あるいは「モスフェット」と呼ばれます。

ソース(S)、ゲート(G)、ドレイン(D)と呼ばれる3つの端子を有しており、ゲートに電圧を加えないとソースとドレイン間に電流は流れません(スイッチがオフの状態です)。ゲートに電圧を加えるとゲート酸化膜直下にチャネルと呼ばれる電子が流れることができる経路が形成され、ソースとドレイン間に電流が流れます(これがスイッチオンの状態です)。

イメージとしては水力発電に使用されるダムが分かりやすいです。ダムに蓄えられた水は、水門を開くと放出されます。MOSFETに置き換えますと、ダムに蓄えられた水がソースで、水門がゲート、排水部分がドレインで水が電子(電流)に相当します。

MOSFETの微細化

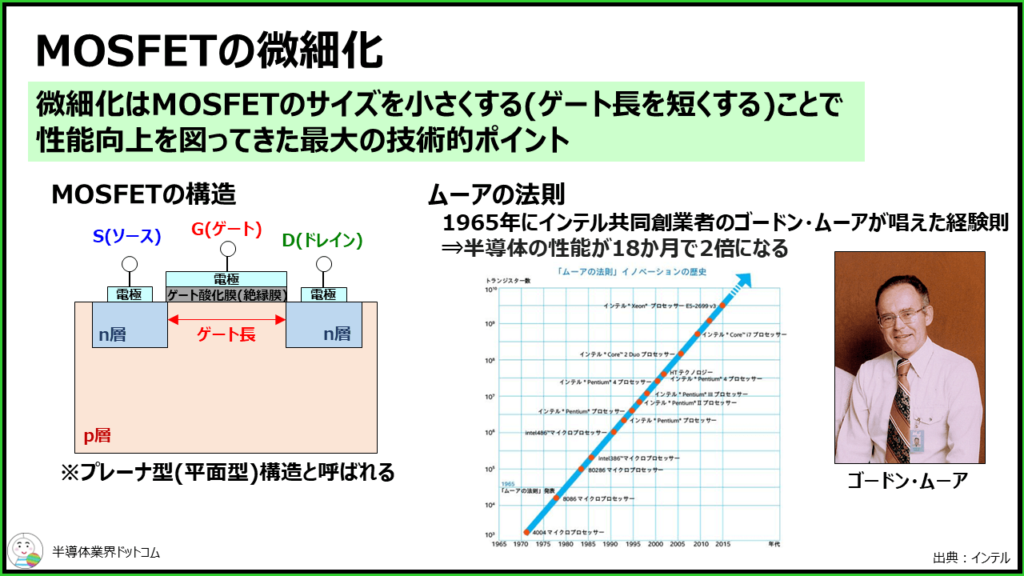

半導体における「微細化」とは、すなわちMOSFETのサイズを小さくする(ゲート長を短くする)ことで性能向上を図ってきた最大の技術的なポイントです。

上図のようなMOSFETはプレーナ型と呼ばれる基本的な構造です。簡単に言いますとこのゲート長を短くすることでトランジスタサイズが小さくなり、同じ面積でより多くのトランジスタを集積できるため、高性能化を図ってきました。

微細化における非常に有名な「ムーアの法則」と呼ばれる法則があります。これは1965年にインテルの共同創業者のひとりであるゴードン・ムーア氏が唱えた経験則で、半導体の性能は18か月から24か月で2倍になるというものです。インテルはこのムーアの法則に従って(言い換えるならばムーアの法則に則るように)微細化を進展させてきました。

「ムーアの法則」

半導体の性能は18か月から24か月で2倍になる

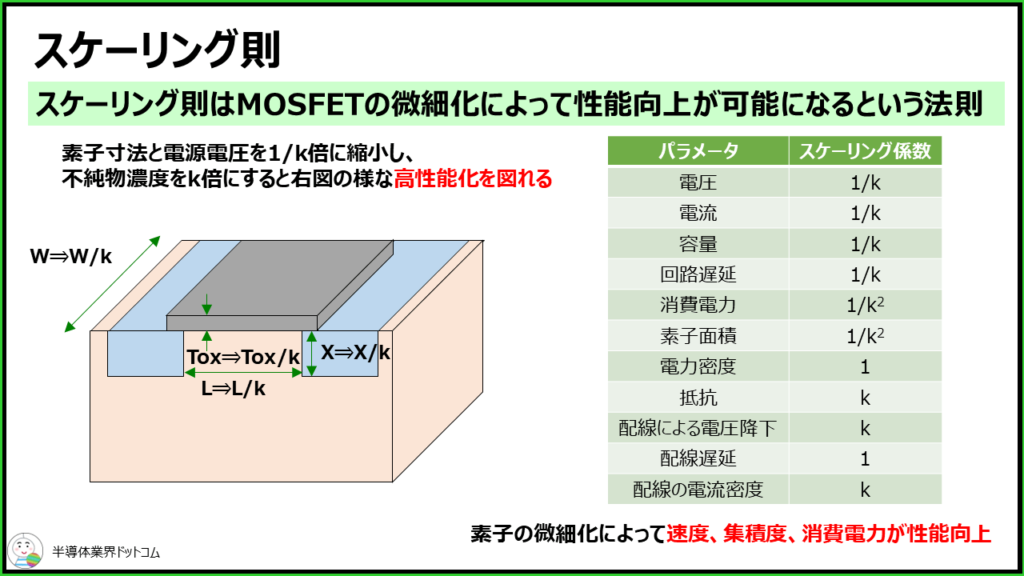

スケーリング則とはMOSFETの微細化による性能向上

MOSFETを微細化することで高性能化を図れることについては「スケーリング則」と呼ばれています。

MOSFETのサイズと電源電圧を1/k倍に縮小し、不純物濃度をk倍とすると、

- 回路遅延が1/k倍になり(すなわち高速化)

- 素子面積は1/kの2乗になり(すなわち集積度向上)

- 消費電力は1/kの2乗になります(すなわち低消費電力化)

実際にはさまざまな課題があり、必ずしもこの理論通りになるわけではありませんが、微細化によって高性能化できることは間違いありませんでした。

「スケーリング則」

トランジスタ(MOSFET)サイズを小さくすることで高性能化が図れること

微細化の限界

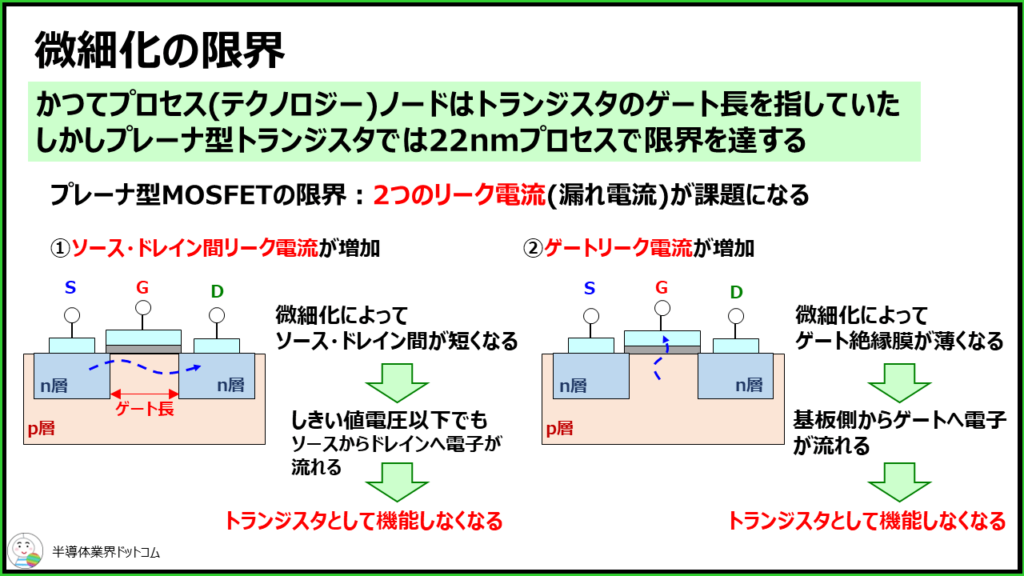

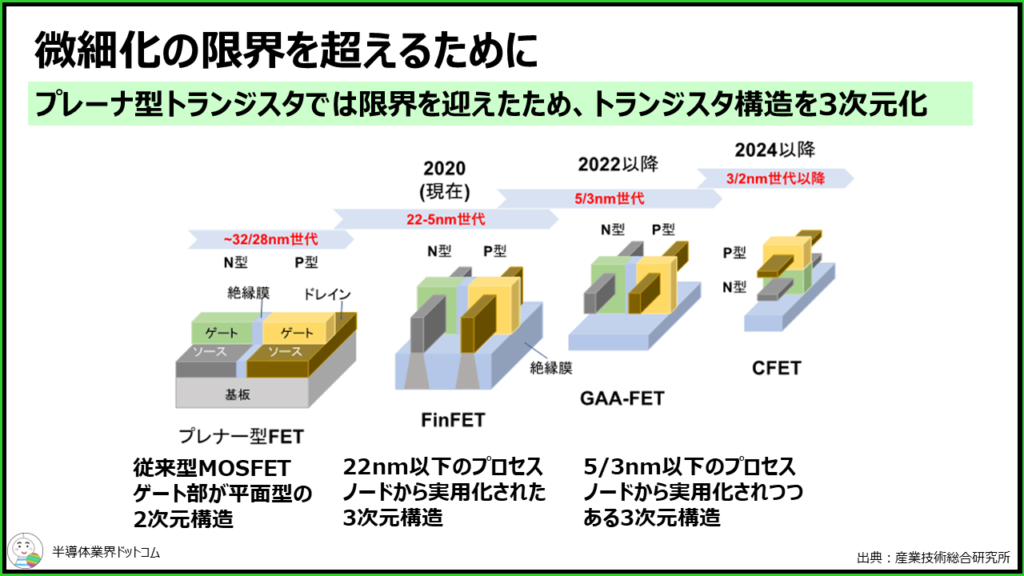

プレーナ型と呼ばれるMOSFET構造において、ゲート長を短くしゲート絶縁膜を薄くする技術開発を続けられてきましたが、22nmプロセス辺りで限界に達しました。

この要因は2つのリーク(漏れ)電流が課題となったためです。

1つ目はソースとドレイン間のリーク電流です。微細化を続けることでソースとドレイン間の距離は当然ながら短くなりました。そうなるとゲートに加える電圧がしきい値と呼ばれる一定の電圧以下であっても電流が流れてしまいトランジスタのスイッチとしての機能を果たせなくなってしまいました。

2つ目はゲートリーク電流です。微細化によってゲート絶縁膜が薄くなることで基板側からゲートへ電子が流れてしまうようになりました。本来であればゲートと基板は絶縁分離されているため、これも大きな問題でした。

微細化の限界を超えるために

プレーナ構造では微細化に限界があるため、トランジスタの構造を変えることで微細化の限界を突破しようと試みられます。研究室レベルであればまだしも、実際の量産に適用する(つまり大規模な回路構造を寸分の狂いなく安定的に生産できる)レベルで実現したことは驚くべきことです。

具体的には以下の3つの構造です。

- FinFET構造(実用化済み)

- GAA構造(最先端品で実用化が進む)

- CFET構造(今後の実用化が期待される)

それでは次に、それぞれの構造の特徴を詳しく見ていきましょう。

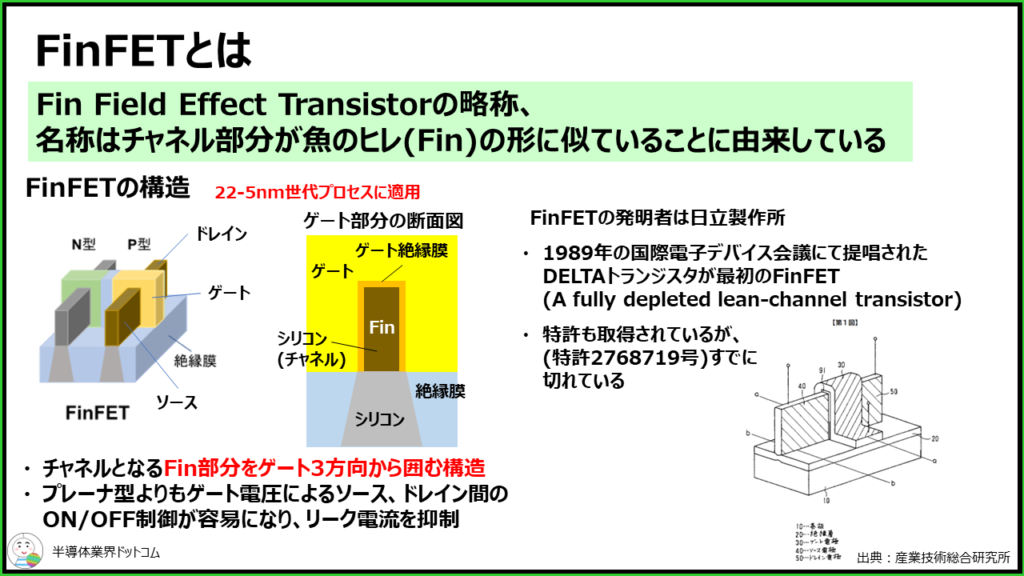

FinFETとは

Fin FET(フィンフェット)のFinとは、チャネル部分が魚のヒレ(Fin)の形に似ていることに由来するトランジスタ構造です。

ソースとドレイン間のチャネル電流を制御するために印加するゲート電圧をチャネルの周囲3方向から加えることで、従来のプレーナ型の限界であった低消費電力化と性能向上の両立を図っています。

Fin FETは日本の日立製作所によって発明され、1989年の国際電子デバイス会議にて提唱されました。特許取得されていますが、すでに切れています。

Fin FETは2010年代に16nmや14nmプロセスでインテルやTSMC、サムスン電子によって実用化されました。

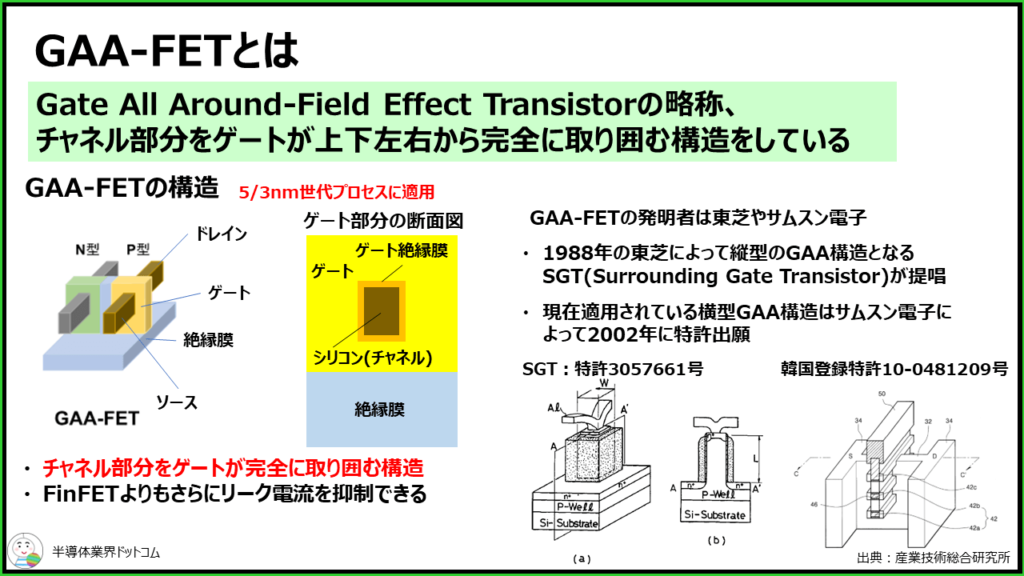

GAA-FETとは

GAAとはGate All Aroundの略称で、その名の通りチャネル部分をゲートが全方向から囲んでいるトランジスタ構造です。

全方位をゲートが取り囲むため、Fin FETよりもさらにリーク電流の抑制が可能となります。

2024年現在であっても数nmプロセスの先端品はほとんどがFin FETで製造されています。2022年7月にサムスン電子が3nm世代プロセスでGAA FETの量産を開始したと公表しているのみです。

TSMCでは2025年に量産を開始するN2と呼ばれるプロセスから適用する見込みです。

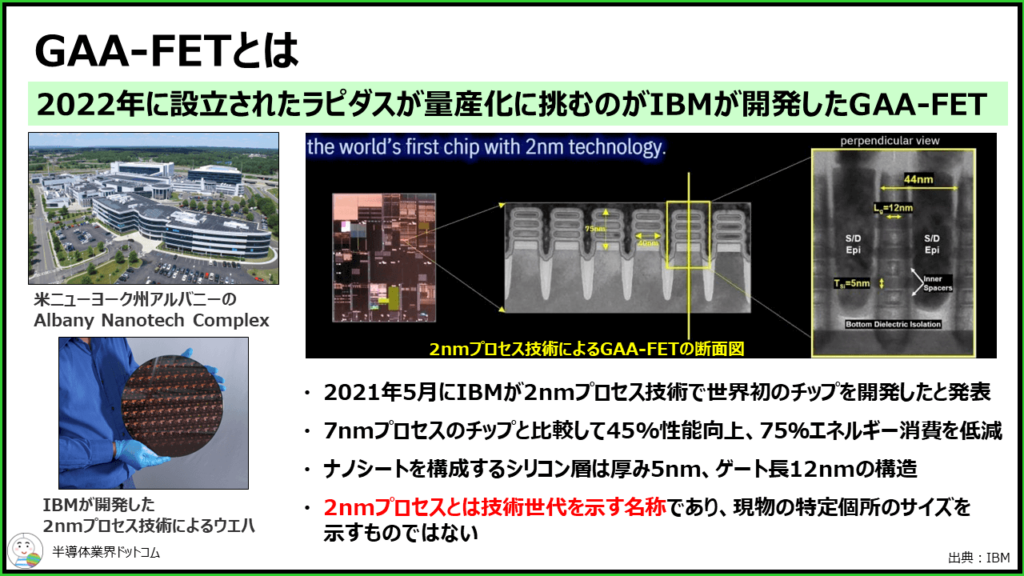

2022年に設立されたラピダスが2027年に量産化を目指しているのが、このGAA FETです。

ラピダスでは米国IBMが2021年に開発に成功したと発表した2nm世代プロセスの量産化を目指しています。ただしここで言う「2nm」とは実際の寸法ではありません。あくまでも技術的な世代を示す名称となっている点に注意が必要です。

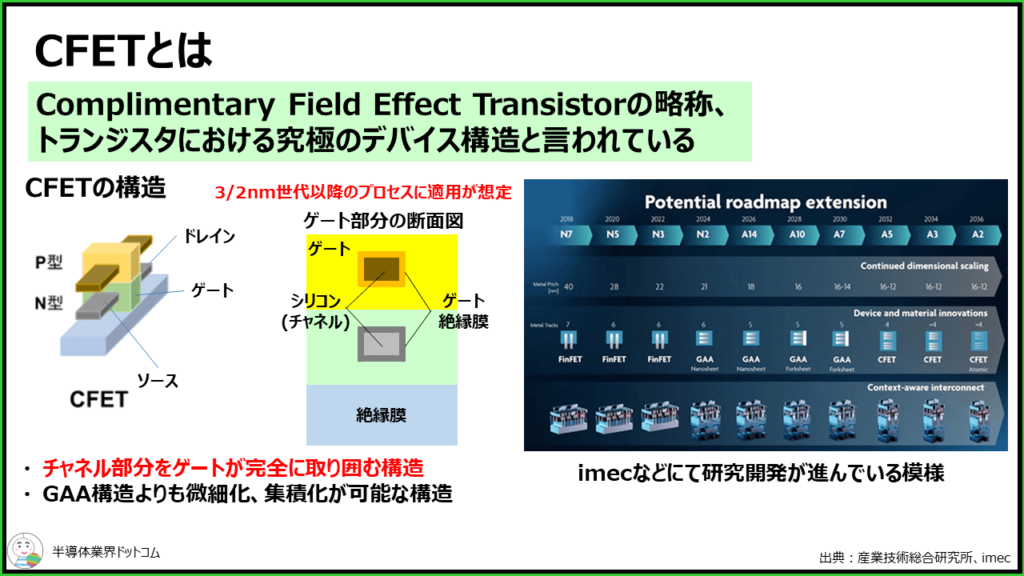

CFETとは

CFETとは、Complementary FETの略称で、2030年代に実用化が期待されているトランジスタ構造です。

GAA FETでは回路の基本となるCMOSを構成するPMOSとNMOSを横並びで構成しますが、CFETではそれを垂直方向に積層して構成します。これによってより一層の微細化・集積化を図ることができるとされています。

2024年現在はimecなどの研究機関で開発が進んでいる模様です。

微細化はどこまで続くのか

今後の先端半導体はどこまで微細化が進むのでしょうか。

過去を振り返ると幾度となく、微細化の限界と言われてきましたが、人類はその壁を乗り越えてきました。これはすなわち、半導体の進化に貢献してきた数多くの研究者、技術者たちの努力の結晶です。

すでに数nmと呼ばれるプロセス世代は、Å(オングストローム)単位が見えてきています。

物理的には原子の大きさは決まっていますので、物理的な限界は必ず訪れます。ただロードマップを見ますと、2035年頃までは進化は続きそうです。具体的な技術論はさておき、今後も人類の知恵とアイデアに期待をしていきたいです。